- 您现在的位置:买卖IC网 > Sheet目录3890 > PIC18C858T-I/PT (Microchip Technology)IC MCU OTP 16KX16 CAN 80TQFP

PIC18CXX8

DS30475A-page 128

Advanced Information

2000 Microchip Technology Inc.

14.1

CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is com-

prised of two 8-bit registers: CCPR1L (low byte) and

CCPR1H (high byte). The CCP1CON register controls

the operation of CCP1. All are readable and writable.

14.2

CCP2 Module

Capture/Compare/PWM Register2 (CCPR2) is com-

prised of two 8-bit registers: CCPR2L (low byte) and

CCPR2H (high byte). The CCP2CON register controls

the operation of CCP2. All are readable and writable.

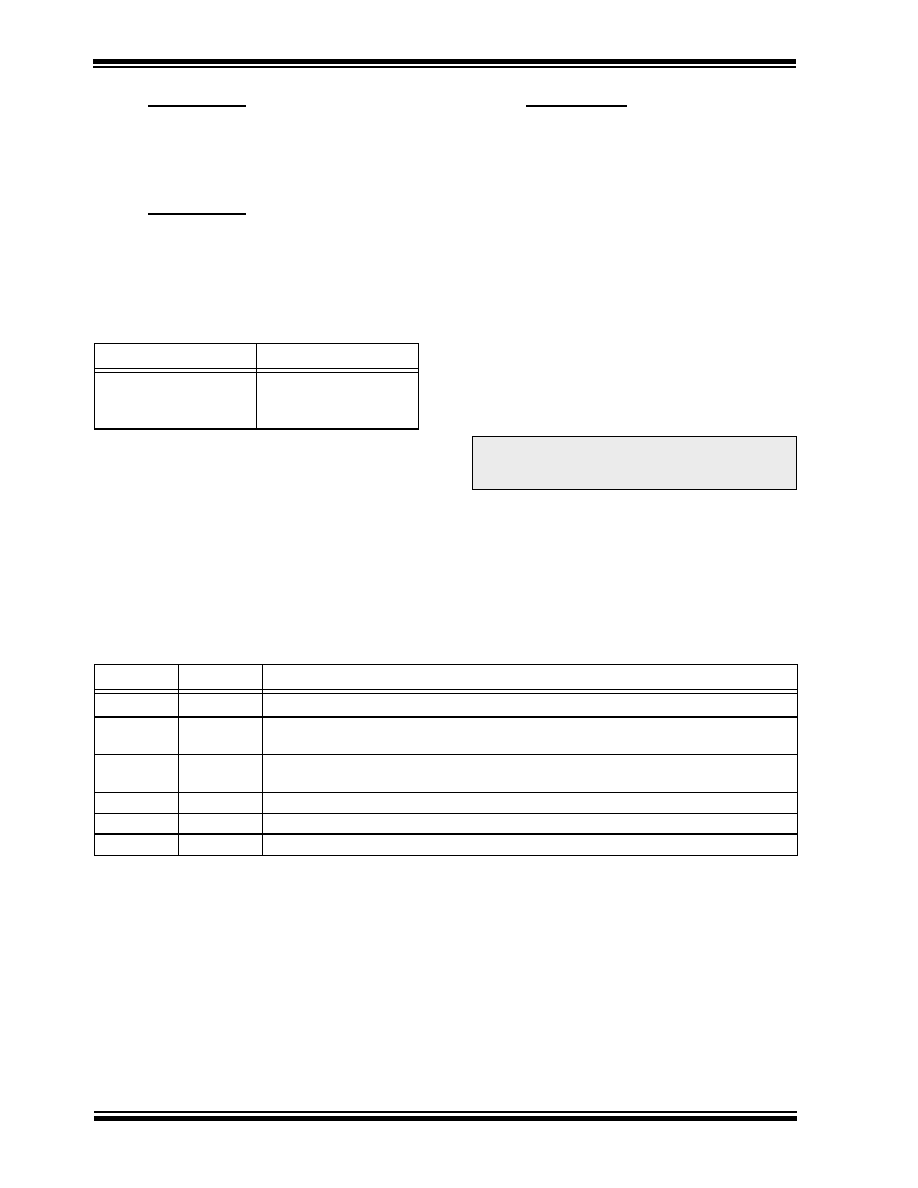

TABLE 14-1:

CCP MODE - TIMER

RESOURCE

14.3

Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the

16-bit value of the TMR1 or TMR3 registers when an

event occurs on pin RC2/CCP1. An event is defined as:

every falling edge

every rising edge

every 4th rising edge

every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0

(CCP1CON<3:0>). When a capture is made, the inter-

rupt request flag bit CCP1IF (PIR registers) is set. It

must be cleared in software. If another capture occurs

before the value in register CCPR1 is read, the old cap-

tured value will be lost.

14.3.1

CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be config-

ured as an input by setting the TRISC<2> bit.

14.3.2

TIMER1/TIMER3 MODE SELECTION

The timers used with the capture feature (either Timer1

and/or Timer3) must be running in Timer mode or Syn-

chronized Counter mode. In Asynchronous Counter

mode, the capture operation may not work. The timer

used with each CCP module is selected in the T3CON

register.

TABLE 14-2:

INTERACTION OF TWO CCP MODULES

CCP Mode

Timer Resource

Capture

Compare

PWM

Timer1 or Timer3

Timer2

Note:

If the RC2/CCP1 is configured as an out-

put, a write to the port can cause a capture

condition.

CCPx Mode CCPy Mode

Interaction

Capture

TMR1 or TMR3 time-base. Time-base can be different for each CCP.

Capture

Compare

The compare could be configured for the special event trigger, which clears either TMR1

or TMR3, depending upon which time-base is used.

Compare

The compare(s) could be configured for the special event trigger, which clears TMR1 or

TMR3 depending upon which time-base is used.

PWM

The PWMs will have the same frequency and update rate (TMR2 interrupt).

PWM

Capture

None

PWM

Compare

None

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18C658T-I/PT

IC MCU OTP 16KX16 CAN 64TQFP

PIC16LC717T-E/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16LC771T/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16LC771T-E/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16C771T-E/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16LC770T/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16LC717T-I/SO

IC MCU OTP 2KX14 A/D PWM 18SOIC

PIC16LC771T/SS

IC MCU OTP 4KX14 A/D PWM 20SSOP

相关代理商/技术参数

PIC18F1220-E/ML

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/P

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/SO

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-E/SS

功能描述:8位微控制器 -MCU 4KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/ML

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/P

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/SO

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F1220-H/SS

功能描述:8位微控制器 -MCU 4KB FL 256RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT